हाय-स्पीड पीसीबी डिझाइनमध्ये कॅपेसिटर महत्त्वाची भूमिका बजावतात आणि बहुतेकदा पीसीबीएसमध्ये सर्वात जास्त वापरले जाणारे उपकरण असतात. पीसीबीमध्ये, कॅपेसिटर सहसा फिल्टर कॅपेसिटर, डीकपलिंग कॅपेसिटर, एनर्जी स्टोरेज कॅपेसिटर इत्यादींमध्ये विभागले जातात.

१.पॉवर आउटपुट कॅपेसिटर, फिल्टर कॅपेसिटर

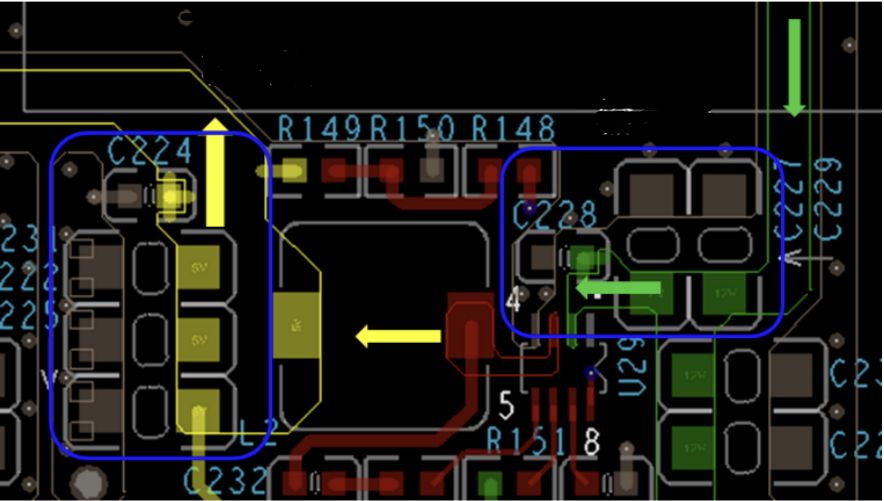

पॉवर मॉड्यूलच्या इनपुट आणि आउटपुट सर्किट्सच्या कॅपेसिटरला आपण सहसा फिल्टर कॅपेसिटर म्हणतो. सोपी समज अशी आहे की कॅपेसिटर इनपुट आणि आउटपुट पॉवर सप्लायची स्थिरता सुनिश्चित करतो. पॉवर मॉड्यूलमध्ये, फिल्टर कॅपेसिटर लहान होण्यापूर्वी मोठा असावा. चित्रात दाखवल्याप्रमाणे, फिल्टर कॅपेसिटर मोठा आणि नंतर बाणाच्या दिशेने लहान ठेवला आहे.

वीज पुरवठ्याची रचना करताना, वायरिंग आणि तांब्याचे कातडे पुरेसे रुंद आहेत आणि प्रवाह क्षमता मागणी पूर्ण करते याची खात्री करण्यासाठी छिद्रांची संख्या पुरेशी आहे हे लक्षात घेतले पाहिजे. रुंदी आणि छिद्रांची संख्या विद्युत प्रवाहाच्या संयोगाने मूल्यांकन केली जाते.

पॉवर इनपुट कॅपेसिटन्स

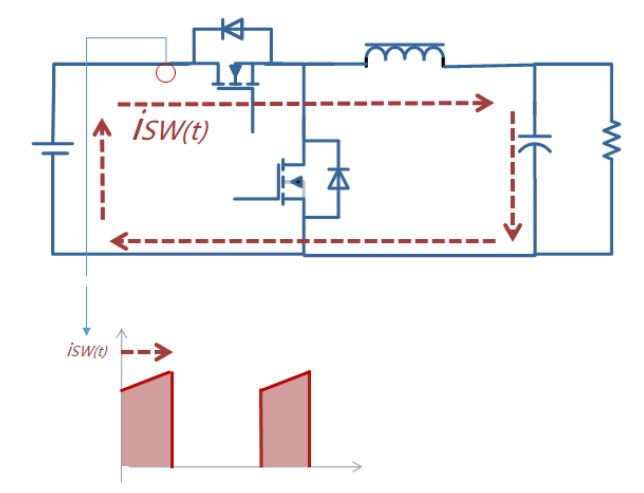

पॉवर इनपुट कॅपेसिटर स्विचिंग लूपसह एक करंट लूप तयार करतो. हा करंट लूप मोठ्या आयाम, आयआउट आयाम नुसार बदलतो. वारंवारता म्हणजे स्विचिंग वारंवारता. डीसीडीसी चिपच्या स्विचिंग प्रक्रियेदरम्यान, या करंट लूपद्वारे निर्माण होणारा करंट बदलतो, ज्यामध्ये वेगवान डाय/डीटीचा समावेश आहे.

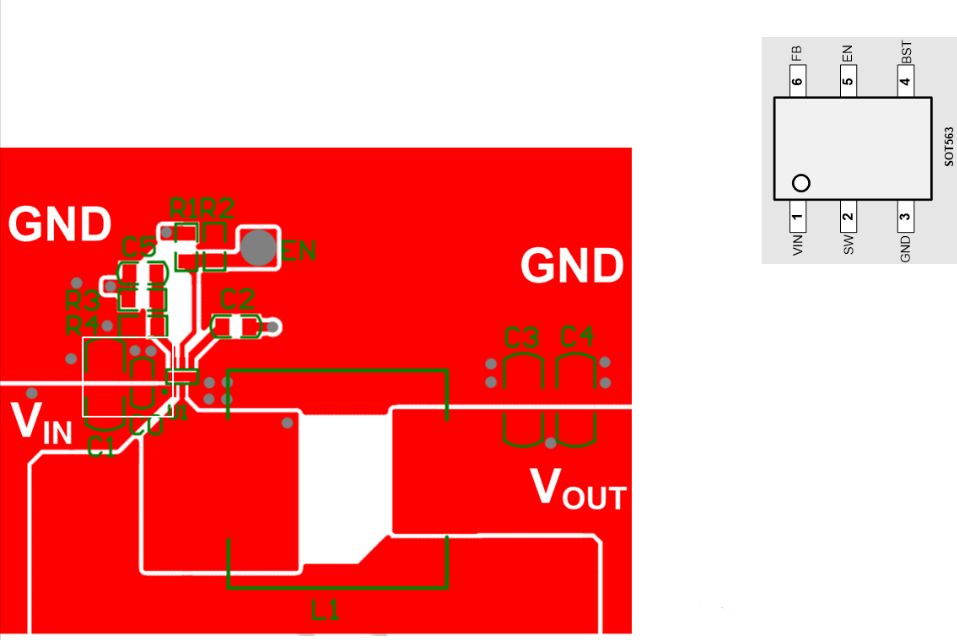

सिंक्रोनस BUCK मोडमध्ये, सतत प्रवाहाचा मार्ग चिपच्या GND पिनमधून गेला पाहिजे आणि इनपुट कॅपेसिटर चिपच्या GND आणि Vin दरम्यान जोडलेला असावा, त्यामुळे मार्ग लहान आणि जाड असू शकतो.

या विद्युत प्रवाहाच्या रिंगचे क्षेत्रफळ पुरेसे लहान आहे, या विद्युत प्रवाहाच्या रिंगचे बाह्य विकिरण जितके चांगले असेल तितके चांगले.

२. डिकपलिंग कॅपेसिटर

हाय-स्पीड आयसीच्या पॉवर पिनला पुरेसे डीकपलिंग कॅपेसिटर आवश्यक असतात, शक्यतो प्रत्येक पिनसाठी एक. प्रत्यक्ष डिझाइनमध्ये, जर डीकपलिंग कॅपेसिटरसाठी जागा नसेल, तर ते योग्यरित्या हटवले जाऊ शकते.

आयसी पॉवर सप्लाय पिनची डीकपलिंग कॅपेसिटन्स सहसा लहान असते, जसे की ०.१μF, ०.०१μF, इ. संबंधित पॅकेज देखील तुलनेने लहान असते, जसे की ०४०२ पॅकेज, ०६०३ पॅकेज इ. डीकपलिंग कॅपेसिटर ठेवताना, खालील मुद्दे लक्षात घेतले पाहिजेत.

(१) पॉवर सप्लाय पिनच्या शक्य तितक्या जवळ ठेवा, अन्यथा त्याचा डीकपलिंग प्रभाव पडणार नाही. सैद्धांतिकदृष्ट्या, कॅपेसिटरमध्ये एक विशिष्ट डीकपलिंग त्रिज्या असते, म्हणून समीपतेचे तत्व काटेकोरपणे अंमलात आणले पाहिजे.

(२) पॉवर सप्लाय पिन लीडला डिकपलिंग कॅपेसिटर शक्य तितका लहान असावा आणि लीड जाड असावा, सहसा रेषेची रुंदी ८ ~ १५ मिली (१ मिली = ०.०२५४ मिमी) असते. जाड करण्याचा उद्देश लीड इंडक्टन्स कमी करणे आणि वीज पुरवठ्याची कार्यक्षमता सुनिश्चित करणे आहे.

(३) डीकपलिंग कॅपेसिटरचे पॉवर सप्लाय आणि ग्राउंड पिन वेल्डिंग पॅडमधून बाहेर काढल्यानंतर, जवळील छिद्रे पंच करा आणि पॉवर सप्लाय आणि ग्राउंड प्लेनला जोडा. शिसे देखील जाड केले पाहिजे आणि छिद्र शक्य तितके मोठे असावे. जर १० मिली छिद्र असलेले छिद्र वापरले जाऊ शकते, तर ८ मिली छिद्र वापरू नये.

(४) डिकपलिंग लूप शक्य तितका लहान असल्याची खात्री करा.

३.ऊर्जा साठवणूक यंत्र

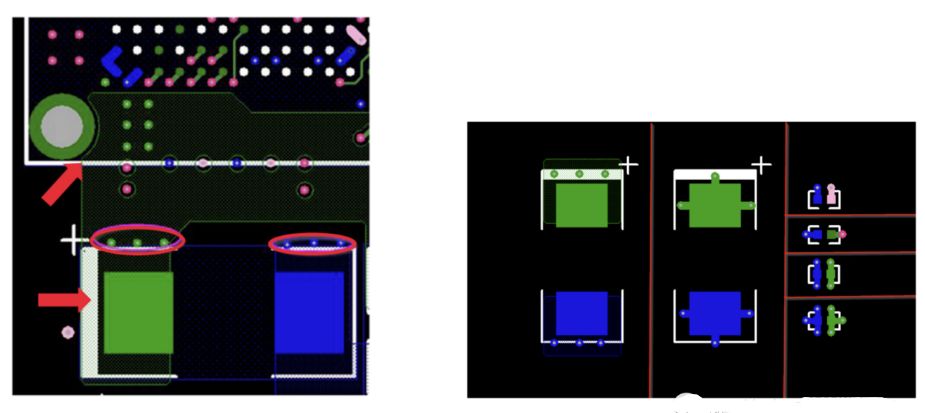

वीज वापरताना आयसी कमीत कमी वेळेत वीज पुरवू शकेल याची खात्री करणे ही ऊर्जा साठवणूक धारकाची भूमिका आहे. ऊर्जा साठवणूक धारकाची क्षमता सामान्यतः मोठी असते आणि संबंधित पॅकेज देखील मोठे असते. पीसीबीमध्ये, ऊर्जा साठवणूक धारका डिव्हाइसपासून खूप दूर असू शकतो, परंतु जास्त दूर नाही, जसे चित्रात दाखवले आहे. सामान्य ऊर्जा साठवणूक धारकाचा फॅन-होल मोड चित्रात दाखवला आहे.

पंख्याच्या छिद्रे आणि केबल्सची तत्त्वे खालीलप्रमाणे आहेत:

(१) शिसे शक्य तितके लहान आणि जाड असावे, जेणेकरून एक लहान परजीवी प्रेरकता असेल.

(२) ऊर्जा साठवणूक कॅपेसिटर किंवा मोठ्या प्रमाणात ओव्हरकरंट असलेल्या उपकरणांसाठी, शक्य तितक्या जास्त छिद्रे करा.

(३) अर्थात, फॅन होलची सर्वोत्तम विद्युत कामगिरी डिस्क होल आहे. वास्तवाचा सर्वसमावेशक विचार करणे आवश्यक आहे.