1. PCB 설계 과정에서 슬롯 형성에는 다음이 포함됩니다.

전원 또는 접지면의 분할로 인한 슬롯팅;PCB에 다양한 전원 공급 장치 또는 접지가 있는 경우 일반적으로 각 전원 공급 장치 네트워크 및 접지 네트워크에 대해 완전한 평면을 할당하는 것은 불가능합니다.일반적인 접근 방식은 여러 평면에서 전력 분할 또는 접지 분할을 수행하는 것입니다.슬롯은 동일한 평면의 서로 다른 분할 사이에 형성됩니다.

관통 구멍은 슬롯을 형성하기에는 너무 조밀합니다(통과 구멍에는 패드와 비아가 포함됨).관통 구멍이 전기적 연결 없이 접지층이나 전원층을 통과할 때 전기 절연을 위해 관통 구멍 주변에 약간의 공간을 남겨 두어야 합니다.하지만 관통 구멍이 서로 너무 가까우면 스페이서 링이 겹쳐서 슬롯이 생성됩니다.

2. 슬롯팅이 PCB 버전의 EMC 성능에 미치는 영향

홈 가공은 PCB 보드의 EMC 성능에 일정한 영향을 미칩니다.이 영향은 부정적일 수도 있고 긍정적일 수도 있습니다.먼저 고속 신호와 저속 신호의 표면 전류 분포를 이해해야 합니다.저속에서 전류는 저항이 가장 낮은 경로를 따라 흐릅니다.아래 그림은 저속 전류가 A에서 B로 흐를 때 반환 신호가 접지면에서 소스로 어떻게 반환되는지 보여줍니다.이때 표면 전류 분포는 더 넓어집니다.

고속에서는 신호 복귀 경로에 대한 인덕턴스의 영향이 저항의 영향을 초과합니다.고속 리턴 신호는 가장 낮은 임피던스의 경로를 따라 흐릅니다.이 때, 표면 전류 분포는 매우 좁고, 반환 신호는 신호 라인 아래에 묶음으로 집중됩니다.

PCB에 호환되지 않는 회로가 있는 경우 "접지 분리" 처리가 필요합니다. 즉, 서로 다른 전원 전압, 디지털 및 아날로그 신호, 고속 및 저속 신호, 고전류에 따라 접지면을 별도로 설정하는 것입니다. 그리고 저전류 신호.위에서 설명한 고속 신호 분포와 저속 신호 복귀를 통해 별도의 접지를 통해 호환되지 않는 회로의 복귀 신호 중첩을 방지하고 공통 접지선 임피던스 결합을 방지할 수 있다는 것을 쉽게 이해할 수 있습니다.

그러나 고속 신호 또는 저속 신호에 관계없이 신호 라인이 전원 플레인 또는 접지 플레인의 슬롯을 교차하면 다음을 포함하여 많은 심각한 문제가 발생합니다.

전류 루프 영역을 늘리면 루프 인덕턴스가 증가하여 출력 파형이 쉽게 진동할 수 있습니다.

엄격한 임피던스 제어가 요구되고 스트립라인 모델에 따라 라우팅되는 고속 신호선의 경우, 상부면 또는 하부면 또는 상부 및 하부면의 슬롯팅으로 인해 스트립라인 모델이 파괴되어 임피던스 불연속 및 심각한 문제가 발생하게 됩니다. 신호 무결성.성적 문제;

우주로의 방사선 방출을 증가시키고 우주 자기장의 간섭을 받기 쉽습니다.

루프 인덕턴스의 고주파수 전압 강하는 공통 모드 방사선 소스를 구성하고 공통 모드 방사선은 외부 케이블을 통해 생성됩니다.

보드의 다른 회로와 고주파 신호 누화 가능성을 높입니다.

PCB에 호환되지 않는 회로가 있는 경우 "접지 분리" 처리가 필요합니다. 즉, 서로 다른 전원 전압, 디지털 및 아날로그 신호, 고속 및 저속 신호, 고전류에 따라 접지면을 별도로 설정하는 것입니다. 그리고 저전류 신호.위에서 설명한 고속 신호 분포와 저속 신호 복귀를 통해 별도의 접지를 통해 호환되지 않는 회로의 복귀 신호 중첩을 방지하고 공통 접지선 임피던스 결합을 방지할 수 있다는 것을 쉽게 이해할 수 있습니다.

그러나 고속 신호 또는 저속 신호에 관계없이 신호 라인이 전원 플레인 또는 접지 플레인의 슬롯을 교차하면 다음을 포함하여 많은 심각한 문제가 발생합니다.

전류 루프 영역을 늘리면 루프 인덕턴스가 증가하여 출력 파형이 쉽게 진동할 수 있습니다.

엄격한 임피던스 제어가 요구되고 스트립라인 모델에 따라 라우팅되는 고속 신호선의 경우, 상부면 또는 하부면 또는 상부 및 하부면의 슬롯팅으로 인해 스트립라인 모델이 파괴되어 임피던스 불연속 및 심각한 문제가 발생하게 됩니다. 신호 무결성.성적 문제;

우주로의 방사선 방출을 증가시키고 우주 자기장의 간섭을 받기 쉽습니다.

루프 인덕턴스의 고주파수 전압 강하는 공통 모드 방사선 소스를 구성하고 공통 모드 방사선은 외부 케이블을 통해 생성됩니다.

보드의 다른 회로와의 고주파 신호 누화 가능성을 높입니다.

3. 슬롯팅을 위한 PCB 설계 방법

홈 가공은 다음 원칙을 따라야 합니다.

엄격한 임피던스 제어가 필요한 고속 신호 라인의 경우, 임피던스 불연속성과 심각한 신호 무결성 문제를 피하기 위해 트레이스가 분할된 라인을 교차하는 것이 엄격히 금지됩니다.

PCB에 호환되지 않는 회로가 있는 경우 접지 분리를 수행해야 하지만 접지 분리로 인해 고속 신호 라인이 분할 배선을 교차하지 않아야 하며 저속 신호 라인이 분할 배선을 교차하지 않도록 해야 합니다.

슬롯 간 라우팅이 불가피할 경우 브리징을 수행해야 합니다.

커넥터(외부)를 접지층에 배치하면 안 됩니다.그림에서 접지층의 A 지점과 B 지점 사이에 큰 전위차가 있는 경우 외부 케이블을 통해 공통 모드 복사가 생성될 수 있습니다.

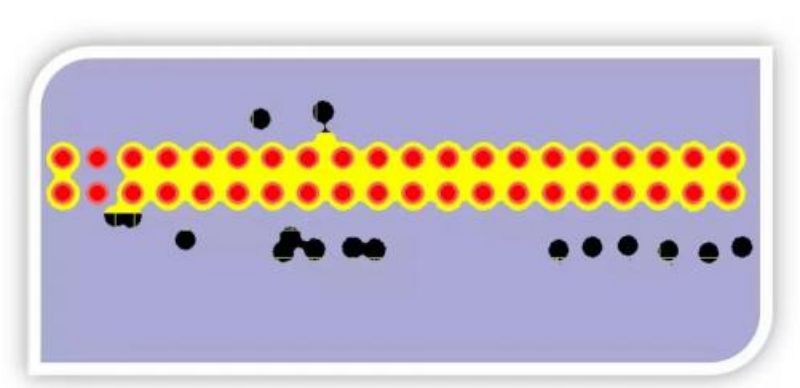

고밀도 커넥터용 PCB를 설계할 때 특별한 요구 사항이 없는 한 일반적으로 접지 네트워크가 각 핀을 둘러싸도록 해야 합니다.핀을 배열할 때 접지면의 연속성을 보장하고 슬롯 생성을 방지하기 위해 접지 네트워크를 균등하게 배열할 수도 있습니다.