Wann maachen dePCB Routing, Wéinst der virleefeg Analyse Aarbecht ass net gemaach oder net gemaach, d'Postveraarbechtung ass schwéier.Wann de PCB Board mat eiser Stad verglach gëtt, sinn d'Komponente wéi Zeil op Zeil vun all Zorte vu Gebaier, Signallinne si Stroossen a Gaassen an der Stad, Flyover Rondpoint Insel, d'Entstoe vun all Strooss ass seng detailléiert Planung, Drot ass och datselwecht.

1. Wiring Prioritéit Ufuerderunge

A) Schlëssel Signal Linnen sinn bevorzugt: Energieversuergung, Analog kleng Signal, Héich-Vitesse Signal, Auer Signal, Synchroniséierung Signal an aner Schlëssel Signaler sinn am léifste.

B) Wiring Dicht Prioritéit Prinzip: Start wiring vun der Komponente mat der komplex Verbindung Relatioun op de Verwaltungsrot.Kabling fänkt aus dem dichtste verbonnen Gebitt um Bord.

C) Virsiichtsmoossnamen fir Schlëssel Signal Veraarbechtung: probéieren eng speziell wiring Layer fir Schlëssel Signaler wéi Auer Signal, héich-Frequenz Signal a sensibel Signal ze bidden, a garantéiert de Minimum Loop Beräich.Wann néideg, soll d'Schirmung an d'Erhéijung vun der Sécherheetsabstand ugeholl ginn.Sécherstellen Signal Qualitéit.

D) D'Netz mat Impedanz Kontroll Ufuerderunge soll op der Impedanz Kontroll Layer arrangéiert ginn, a seng Signal Kräiz-Divisioun soll verhënnert ginn.

2.Wiring scrambler Kontroll

A) Interpretatioun vum 3W Prinzip

D'Distanz tëscht de Linnen soll 3 Mol d'Linn Breet sinn.Fir Crosstalk tëscht Zeilen ze reduzéieren, soll d'Linnabstand grouss genuch sinn.Wann d'Linnzentrumdistanz net manner wéi 3 Mol d'Linnbreed ass, kënnen 70% vum elektresche Feld tëscht Linnen ouni Interferenz gehale ginn, wat d'3W Regel genannt gëtt.

B) Tampering Kontroll: CrossTalk bezitt sech op déi géigesäiteg Amëschung tëscht verschiddene Netzwierker op PCB verursaacht duerch laang parallele Verdrahtung, haaptsächlech wéinst der Handlung vun verdeeler Kapazitéit a verdeelt Induktioun tëscht parallele Linnen.D'Haaptmoossname fir Crosstalk ze iwwerwannen sinn:

I. Vergréisseren d'Distanz vun parallel cabling a befollegen der 3W Regel;

Ii.Setzt d'Grondisolatiounskabel tëscht parallele Kabelen

Iii.Reduzéiert d'Distanz tëscht der Kabelschicht an dem Buedemplang.

3. Allgemeng Regele fir wiring Ufuerderunge

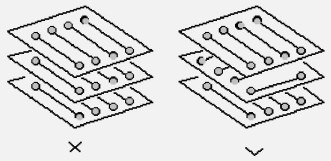

A) D'Richtung vun der Nopeschfläch ass orthogonal.Vermeit déi verschidde Signallinnen an der Nopeschschicht an der selwechter Richtung fir onnéideg Inter-Layer Tampering ze reduzéieren;Wann dës Situatioun schwéier ze vermeiden ass wéinst Verwaltungsrot Struktur Aschränkungen (wéi e puer backplanes), virun allem wann d'Signal Taux héich ass, Dir sollt isoléieren wiring Schichten um Buedem Fliger betruecht an Signal Kabelen um Buedem.

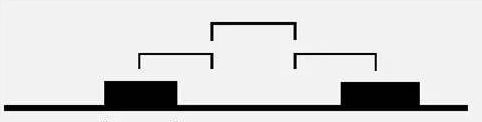

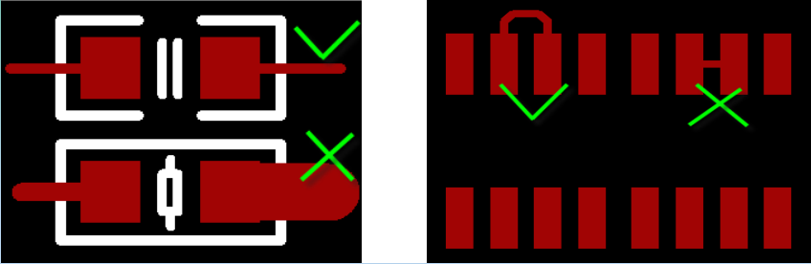

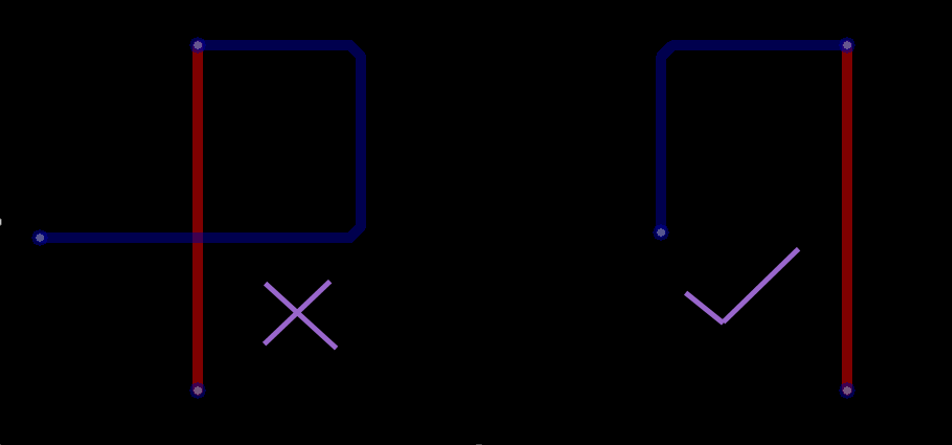

B) D'Verdrahtung vu klengen diskreten Apparater muss symmetresch sinn, an d'SMT Pad Leads mat relativ enke Abstand solle vu baussen vum Pad verbonne sinn.Direkt Verbindung an der Mëtt vum Pad ass net erlaabt.

C) Minimum Loop Regel, dat heescht, d'Gebitt vun der Loop geformt vun der Signallinn a seng Loop soll esou kleng wéi méiglech sinn.Wat méi kleng d'Gebitt vun der Loop ass, wat manner déi extern Stralung a wat méi kleng ass déi extern Interferenz.

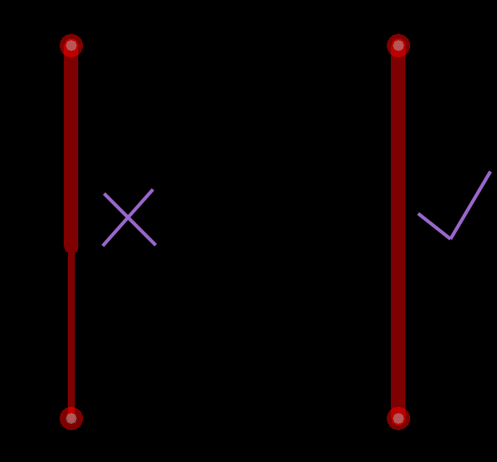

D) STUB Kabelen sinn net erlaabt

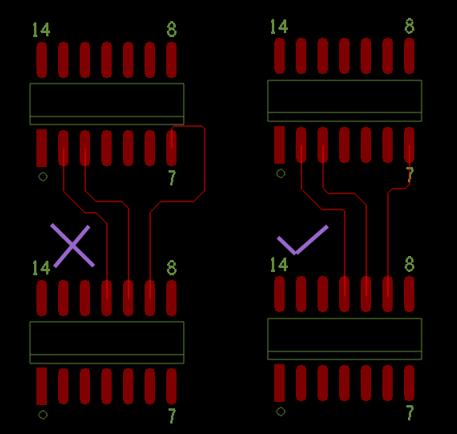

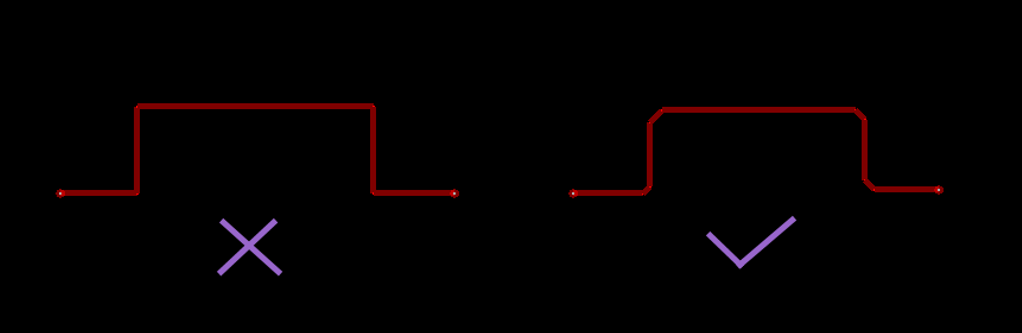

E) D'Wiring Breet vun der selwechter Reseau soll déi selwecht gehaalen gin.D'Variatioun vun der Wiring Breet wäert déi ongläich charakteristesch Impedanz vun der Linn verursaachen.Wann d'Transmissiounsgeschwindegkeet héich ass, wäert Reflexioun optrieden.Ënner e puer Konditiounen, wéi de Stecker Féierung Drot, BGA Package Féierung Drot ähnlech Struktur, well vun der kleng Abstand net fäheg sinn d'Ännerung vun Linn Breet ze vermeiden, soll probéieren d'efficace Längt vun der Mëtt inkonsequent Deel ze reduzéieren.

F) Verhënnert datt d'Signalkabel Selbstschleifen tëscht verschiddene Schichten bilden.Dës Zort vu Problem ass einfach am Design vun multilayer Placke ze geschéien, an der Self-Loop wäert Stralung Amëschen Ursaach.

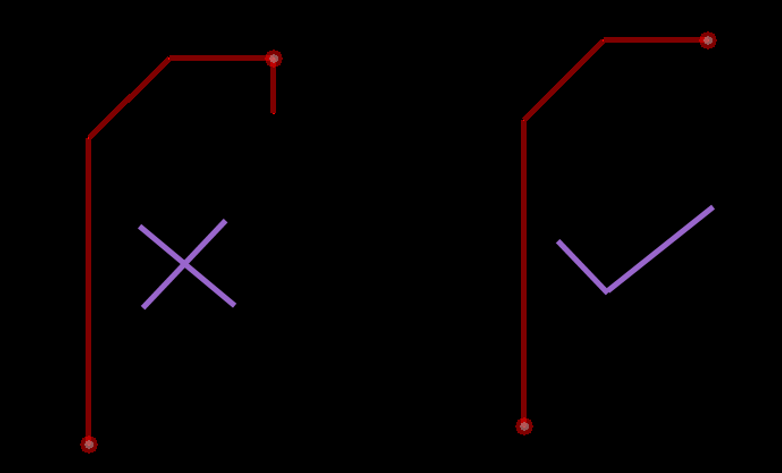

G) Akute Wénkel a richtege Wénkel sollen vermeit ginnPCB Design, doraus an onnéideg Stralung, an der Produktioun Prozess Leeschtung vunPCBass net gutt.