यदि अंतरपरत धारिता पर्याप्त रूप से बड़ी नहीं है, तो विद्युत क्षेत्र बोर्ड के अपेक्षाकृत बड़े क्षेत्र में वितरित हो जाएगा, जिससे अंतरपरत प्रतिबाधा कम हो जाएगी और वापसी धारा ऊपरी परत में वापस प्रवाहित हो सकेगी। इस स्थिति में, इस सिग्नल द्वारा उत्पन्न क्षेत्र निकटवर्ती परिवर्तनशील परत सिग्नल के क्षेत्र में हस्तक्षेप कर सकता है। यह वह नहीं है जिसकी हमें बिल्कुल भी उम्मीद थी। दुर्भाग्य से, 0.062 इंच के 4-परत बोर्ड पर, परतें एक-दूसरे से बहुत दूर हैं और अंतरपरत धारिता कम है।

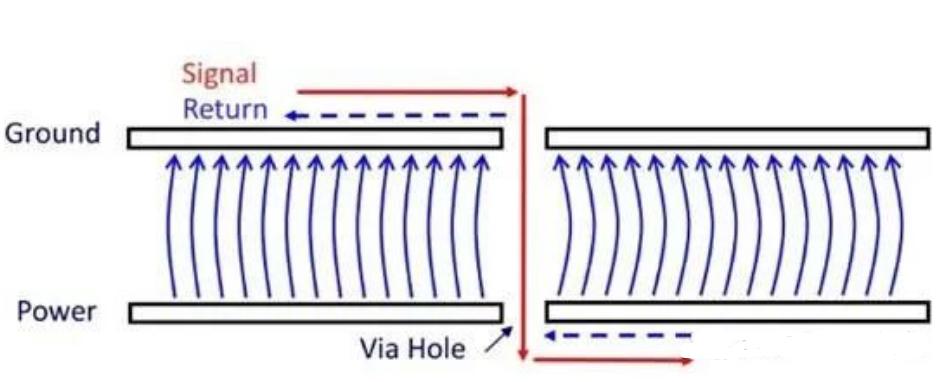

जब वायरिंग लेयर 1 से लेयर 4 या इसके विपरीत बदलती है, तो चित्र में दिखाई गई यह समस्या उत्पन्न होगी

आरेख दर्शाता है कि जब सिग्नल परत 1 से परत 4 (लाल रेखा) तक जाता है, तो वापसी धारा का तल भी बदलना चाहिए (नीली रेखा)। यदि सिग्नल की आवृत्ति पर्याप्त उच्च है और तल एक-दूसरे के निकट हैं, तो वापसी धारा भू-स्तर और विद्युत स्तर के बीच स्थित अंतर-स्तर धारिता से होकर प्रवाहित हो सकती है। हालाँकि, वापसी धारा के लिए प्रत्यक्ष चालकीय संबंध के अभाव में, वापसी पथ बाधित होता है, और हम इस रुकावट को तलों के बीच प्रतिबाधा के रूप में देख सकते हैं, जैसा कि नीचे चित्र में दिखाया गया है।

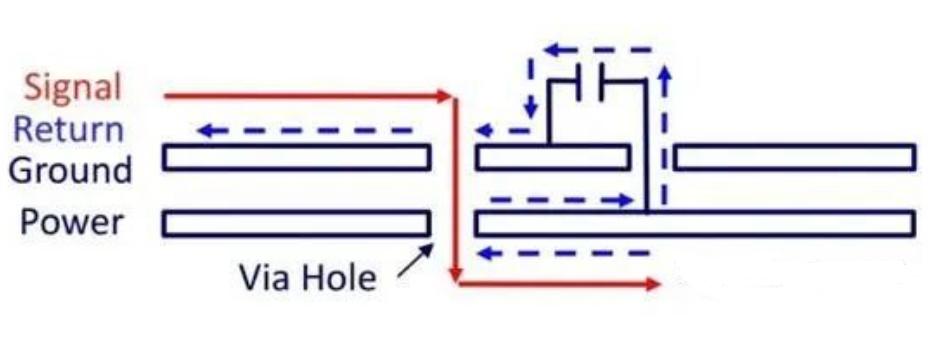

यदि इंटरलेयर कैपेसिटेंस पर्याप्त रूप से बड़ी नहीं है, तो विद्युत क्षेत्र बोर्ड के अपेक्षाकृत बड़े क्षेत्र में वितरित किया जाएगा, ताकि इंटरलेयर प्रतिबाधा कम हो जाए और रिटर्न करंट शीर्ष परत में वापस प्रवाहित हो सके। इस स्थिति में, इस सिग्नल द्वारा उत्पन्न क्षेत्र पास के बदलते लेयर सिग्नल के क्षेत्र में हस्तक्षेप कर सकता है। यह वह नहीं है जिसकी हमें बिल्कुल उम्मीद थी। दुर्भाग्य से, 0.062 इंच के 4-लेयर बोर्ड पर, परतें बहुत दूर (कम से कम 0.020 इंच) होती हैं, और इंटरलेयर कैपेसिटेंस छोटा होता है। नतीजतन, ऊपर वर्णित विद्युत क्षेत्र का हस्तक्षेप होता है। यह सिग्नल अखंडता के मुद्दों का कारण नहीं हो सकता है, लेकिन यह निश्चित रूप से अधिक ईएमआई पैदा करेगा। यही कारण है कि, कैस्केड का उपयोग करते समय, हम परतों को बदलने से बचते हैं

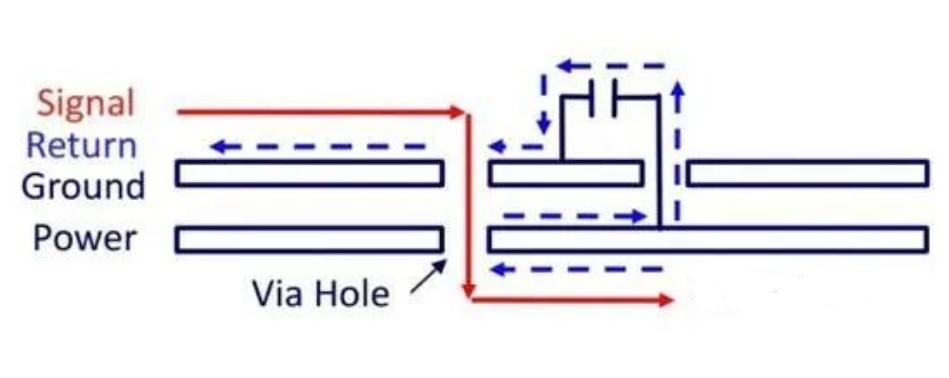

नीचे दिए गए चित्र में दर्शाए गए रिटर्न करंट द्वारा अनुभव की जाने वाली प्रतिबाधा को कम करने के लिए ट्रांज़िशन पास होल के पास एक डिकप्लिंग कैपेसिटर लगाना आम बात है। हालाँकि, यह डिकप्लिंग कैपेसिटर अपनी कम स्व-अनुनाद आवृत्ति के कारण VHF सिग्नल के लिए अप्रभावी है। 200-300 मेगाहर्ट्ज से अधिक आवृत्तियों वाले AC सिग्नल के लिए, हम कम-प्रतिबाधा रिटर्न पथ बनाने के लिए डिकप्लिंग कैपेसिटर पर निर्भर नहीं रह सकते। इसलिए, हमें एक डिकप्लिंग कैपेसिटर (200-300 मेगाहर्ट्ज से कम आवृत्तियों के लिए) और उच्च आवृत्तियों के लिए एक अपेक्षाकृत बड़े इंटरबोर्ड कैपेसिटर की आवश्यकता होती है।

कुंजी सिग्नल की परत को न बदलकर इस समस्या से बचा जा सकता है। हालाँकि, चार-परत वाले बोर्ड की कम अंतर-बोर्ड धारिता एक और गंभीर समस्या का कारण बनती है: विद्युत संचरण। क्लॉक डिजिटल आईसी को आमतौर पर बड़ी क्षणिक विद्युत आपूर्ति धाराओं की आवश्यकता होती है। जैसे-जैसे आईसी आउटपुट का वृद्धि/गिरावट समय घटता है, हमें उच्च दर पर ऊर्जा प्रदान करने की आवश्यकता होती है। आवेश स्रोत प्रदान करने के लिए, हम आमतौर पर प्रत्येक लॉजिक आईसी के बहुत करीब वियुग्मन संधारित्र लगाते हैं। हालाँकि, एक समस्या है: जब हम स्व-अनुनाद आवृत्तियों से आगे बढ़ जाते हैं, तो वियुग्मन संधारित्र ऊर्जा को कुशलतापूर्वक संग्रहीत और स्थानांतरित नहीं कर पाते, क्योंकि इन आवृत्तियों पर संधारित्र एक प्रेरक की तरह कार्य करेगा।

चूँकि आजकल अधिकांश आईसी का अपवर्तन/पतन समय तेज़ होता है (लगभग 500 ps), हमें वियुग्मन संधारित्र की तुलना में उच्च स्व-अनुनाद आवृत्ति वाली एक अतिरिक्त वियुग्मन संरचना की आवश्यकता होती है। एक सर्किट बोर्ड की अंतरपरत धारिता एक प्रभावी वियुग्मन संरचना हो सकती है, बशर्ते कि परतें पर्याप्त धारिता प्रदान करने के लिए एक-दूसरे के पर्याप्त निकट हों। इसलिए, सामान्यतः प्रयुक्त वियुग्मन संधारित्रों के अतिरिक्त, हम डिजिटल आईसी को क्षणिक शक्ति प्रदान करने के लिए निकट-अंतरित शक्ति परतों और भू-परतों का उपयोग करना पसंद करते हैं।

कृपया ध्यान दें कि सामान्य सर्किट बोर्ड निर्माण प्रक्रिया के कारण, आमतौर पर चार-परत वाले बोर्ड की दूसरी और तीसरी परतों के बीच पतले इंसुलेटर नहीं होते हैं। दूसरी और तीसरी परतों के बीच पतले इंसुलेटर वाले चार-परत वाले बोर्ड की कीमत पारंपरिक चार-परत वाले बोर्ड की तुलना में बहुत अधिक हो सकती है।