층간 정전용량이 충분히 크지 않으면 전기장이 기판의 비교적 넓은 영역에 분산되어 층간 임피던스가 감소하고 귀환 전류가 최상층으로 다시 흐를 수 있습니다. 이 경우, 이 신호에 의해 생성된 전기장은 인근 변화층 신호의 전기장을 간섭할 수 있습니다. 이는 우리가 기대했던 바와는 전혀 다릅니다. 안타깝게도 0.062인치 두께의 4층 기판에서는 각 층이 서로 멀리 떨어져 있고 층간 정전용량이 작습니다.

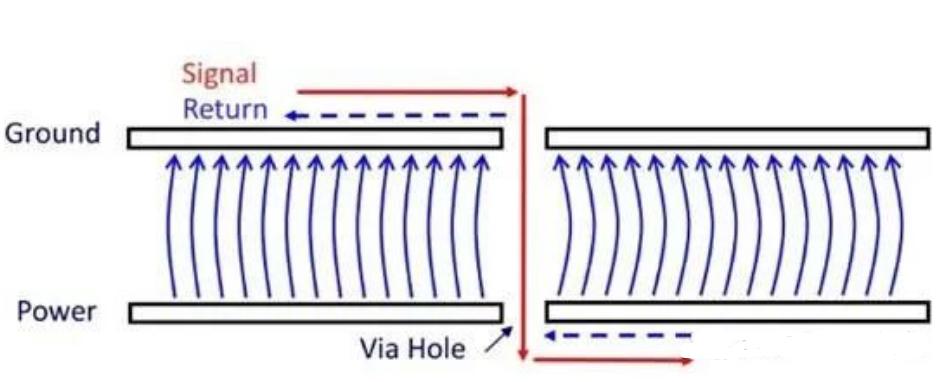

배선이 레이어 1에서 레이어 4로 변경되거나 그 반대로 변경될 때 그림과 같이 이 문제가 발생합니다.

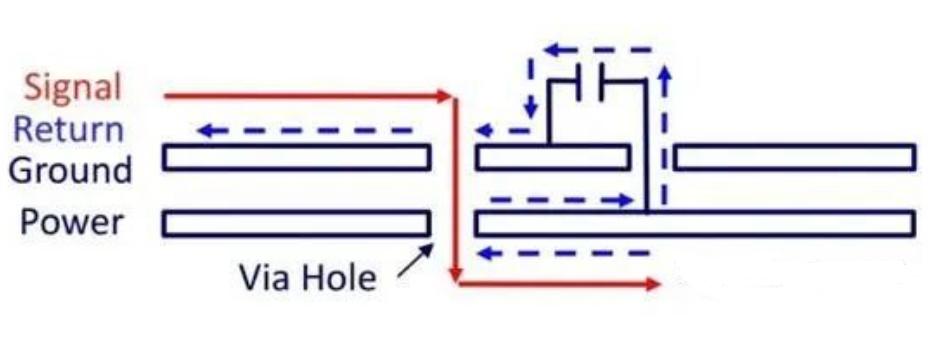

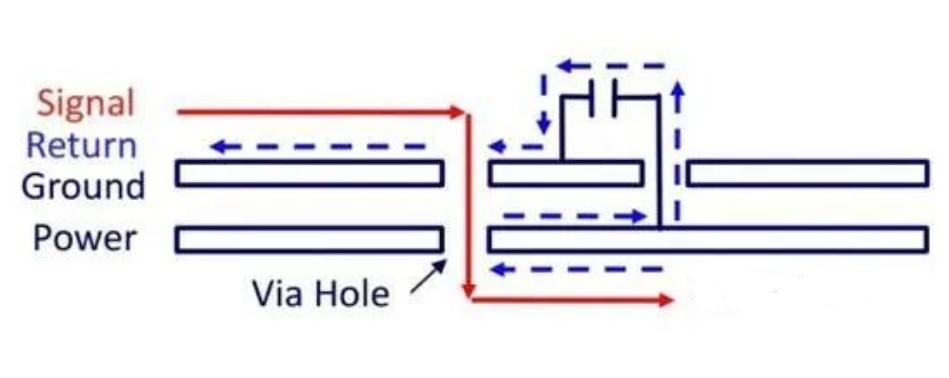

그림은 신호가 1층에서 4층(빨간색 선)으로 이동할 때 귀환 전류도 평면(파란색 선)으로 변해야 함을 보여줍니다. 신호 주파수가 충분히 높고 평면들이 서로 가까이 있으면 귀환 전류는 접지층과 전력층 사이에 존재하는 층간 커패시턴스를 통해 흐를 수 있습니다. 그러나 귀환 전류에 대한 직접적인 전도 연결이 없기 때문에 귀환 경로가 차단되며, 이러한 차단은 아래 그림과 같이 평면들 사이의 임피던스로 생각할 수 있습니다.

층간 캐패시턴스가 충분히 크지 않으면 전기장이 보드의 비교적 넓은 영역에 분산되어 층간 임피던스가 감소하고 귀환 전류가 최상층으로 다시 흐를 수 있습니다. 이 경우, 이 신호에 의해 생성된 전기장은 인근 변화층 신호의 전기장을 간섭할 수 있습니다. 이는 우리가 전혀 기대하지 않았던 결과입니다. 안타깝게도 0.062인치 두께의 4층 보드에서는 각 층이 서로 멀리 떨어져 있고(최소 0.020인치), 층간 캐패시턴스가 작습니다. 결과적으로 위에서 설명한 전기장 간섭이 발생합니다. 이는 신호 무결성 문제를 일으키지 않을 수 있지만, 확실히 더 많은 EMI를 발생시킵니다. 이것이 캐스케이드를 사용할 때, 특히 클록과 같은 고주파 신호의 경우 층 변경을 피하는 이유입니다.

아래 그림과 같이 귀환 전류로 인한 임피던스를 줄이기 위해 전이 패스 홀 근처에 디커플링 커패시터를 추가하는 것이 일반적입니다. 그러나 이 디커플링 커패시터는 자기 공진 주파수가 낮아 VHF 신호에는 효과적이지 않습니다. 200~300MHz보다 높은 주파수의 AC 신호의 경우, 디커플링 커패시터만으로는 저임피던스 귀환 경로를 생성할 수 없습니다. 따라서 200~300MHz 미만용 디커플링 커패시터와 더 높은 주파수용 비교적 큰 보드 간 커패시터가 필요합니다.

이 문제는 키 신호의 계층을 변경하지 않으면 해결할 수 있습니다. 그러나 4층 기판의 작은 기판 간 정전용량은 전력 전송이라는 또 다른 심각한 문제를 야기합니다. 클록 디지털 IC는 일반적으로 큰 과도 전원 공급 전류를 필요로 합니다. IC 출력의 상승/하강 시간이 감소함에 따라 더 높은 속도로 에너지를 공급해야 합니다. 충전 소스를 제공하기 위해 일반적으로 각 로직 IC에 매우 가깝게 디커플링 커패시터를 배치합니다. 그러나 한 가지 문제가 있습니다. 자기 공진 주파수를 초과하면 디커플링 커패시터가 에너지를 효율적으로 저장하고 전송할 수 없습니다. 이 주파수에서는 커패시터가 인덕터처럼 동작하기 때문입니다.

오늘날 대부분의 IC는 빠른 상승/하강 시간(약 500ps)을 가지므로, 디커플링 커패시터보다 더 높은 자기공진 주파수를 갖는 추가적인 디커플링 구조가 필요합니다. 회로 기판의 층간 커패시턴스는 각 층이 서로 충분히 가까워 충분한 커패시턴스를 제공할 수 있다면 효과적인 디커플링 구조가 될 수 있습니다. 따라서 일반적으로 사용되는 디커플링 커패시터 외에도, 전력층과 접지층을 가깝게 배치하여 디지털 IC에 과도 전력을 공급하는 방식을 선호합니다.

일반적인 회로 기판 제조 공정으로 인해 4층 기판의 두 번째 층과 세 번째 층 사이에는 일반적으로 얇은 절연체가 없습니다. 두 번째 층과 세 번째 층 사이에 얇은 절연체가 있는 4층 기판은 기존 4층 기판보다 훨씬 비쌀 수 있습니다.