Beim Layoutdesign vun der PCB ass d'Layout vun de Komponenten entscheedend, wat den ordentlechen a schéine Grad vun der Platin an d'Längt an d'Quantitéit vum gedréckte Drot bestëmmt, an e gewëssen Afloss op d'Zouverlässegkeet vun der ganzer Maschinn huet.

Eng gutt Leiterplat, nieft der Ëmsetzung vum Funktiounsprinzip, muss och EMI, EMC, ESD (elektrostatesch Entladung), Signalintegritéit an aner elektresch Charakteristiken berécksiichtegt ginn, awer och d'mechanesch Struktur an d'Hëtztofléisungsproblemer vu grousse Stroumchips berécksiichtegt ginn.

Allgemeng Ufuerderunge fir d'Spezifikatioun vum PCB-Layout

1, liest d'Designbeschreiwungsdokument, erfëllt déi speziell Struktur, de spezielle Modul an aner Layoutufuerderungen.

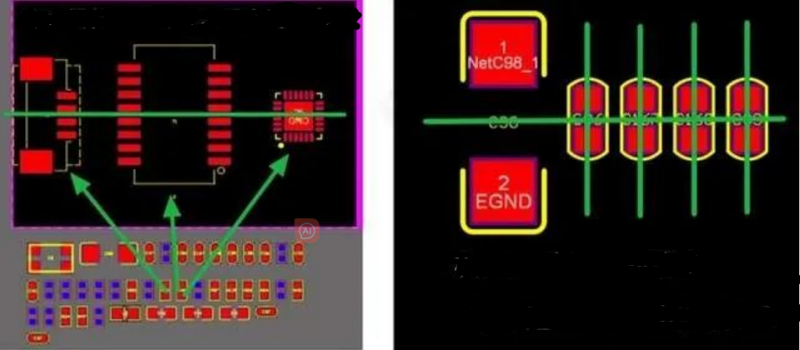

2, setzt de Layout-Rasterpunkt op 25mil, kann iwwer de Rasterpunkt ausgeriicht ginn, gläichen Ofstand; Den Ausriichtungsmodus ass grouss virum klengen (grouss Geräter a grouss Geräter ginn als éischt ausgeriicht), an den Ausriichtungsmodus ass zentral, wéi an der folgender Figur gewisen.

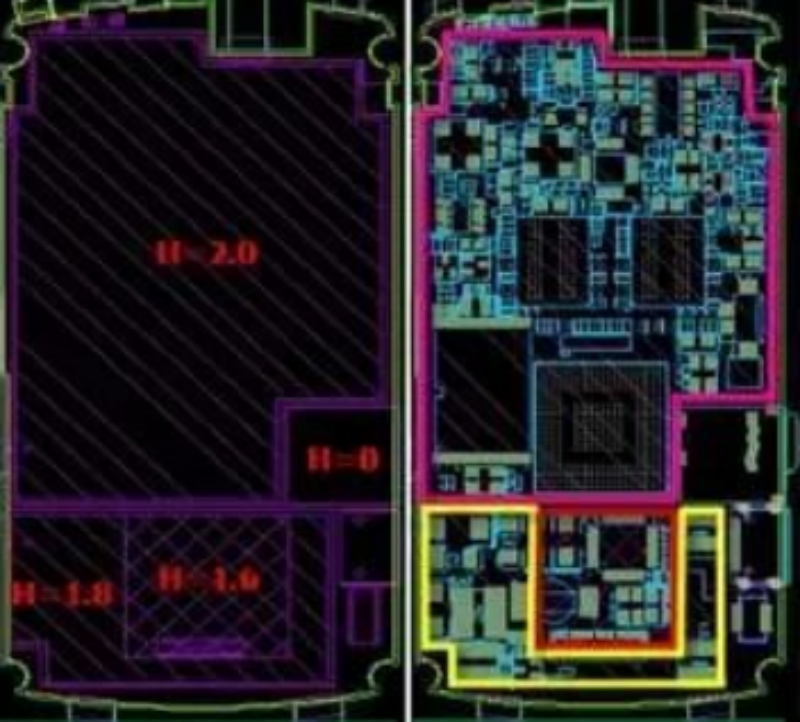

3, erfëllt d'Héichtlimit fir verbueden Zonen, d'Struktur an d'Layout vun engem speziellen Apparat, souwéi d'Ufuerderunge fir verbueden Zonen.

① Figur 1 (lénks) ënnen: Ufuerderunge fir d'Héichtlimit, kloer an der mechanescher Schicht oder der Markéierungsschicht markéiert, praktesch fir spéider Kräizkontrollen;

(2) Virum Ausbau, definéiert de verbuedene Beräich, wouduerch den Apparat 5 mm vum Rand vun der Plack ewech muss sinn, den Apparat net ausbauen, ausser speziell Ufuerderungen oder en spéideren Design vun der Plack kënnen eng Prozesskant derbäisetzen;

③ D'Layout vun der Struktur a speziellen Apparater kann präzis duerch Koordinaten oder duerch d'Koordinaten vum äusseren Kader oder d'Mëttlinn vun de Komponenten positionéiert ginn.

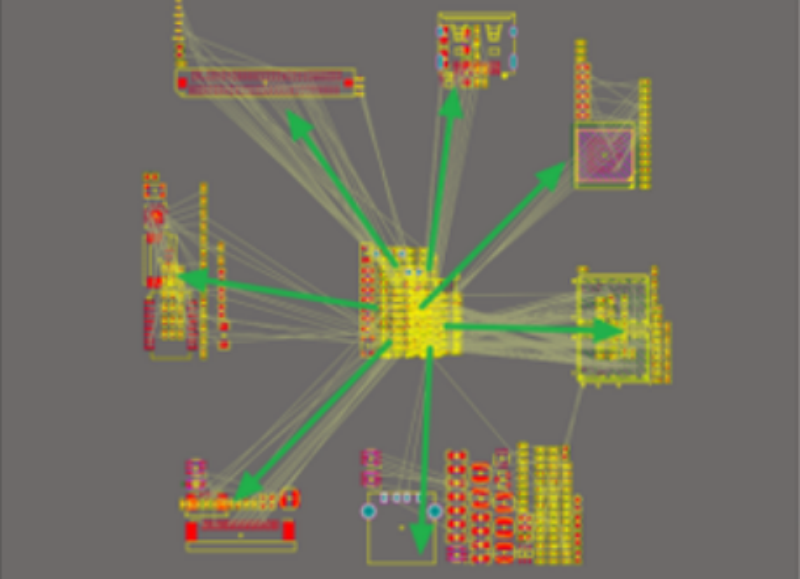

4, De Layout soll als éischt e Virlayout hunn, net direkt mam Layout vum Board ufänken. De Virlayout kann op Basis vum Modulgräifen gemaach ginn, fir d'Linnsignalflussanalyse op der PCB-Plack ze zéien, an dann op Basis vun der Signalflussanalyse d'Hëlleflinn vum Modul op der PCB-Plack ze zéien, fir déi ongeféier Positioun vum Modul op der PCB an d'Gréisst vum Besetzungsberäich ze evaluéieren. Zeechent d'Hëlleflinnbreet vun 40mil, an evaluéiert d'Rationalitéit vum Layout tëscht Moduler a Moduler duerch déi uewe genannten Operatiounen, wéi an der Figur hei ënnendrënner gewisen.

5, beim Layout muss de Kanal berücksichtegt ginn, deen aus der Stroumleitung erausgeet. Et soll net ze enk an ze dicht sinn. Duerch d'Planung muss erausfonnt ginn, wou d'Energie hierkënnt a wou se hi soll goen. De Stroumbam muss gekämmt ginn.

6, D'Layout vun thermesche Komponenten (wéi Elektrolytkondensatoren, Kristalloszillatoren) soll sou wäit ewech vun der Stroumversuergung an aneren héichthermesche Geräter sinn, sou wäit wéi méiglech an der ieweschter Entlüftung.

7, fir déi sensibel Moduldifferenzéierung, d'Gläichgewiicht vum ganze Board-Layout an d'Reservatioun vun der ganzer Board-Verdrahtungskanal ze erfëllen.

D'Héichspannungs- an Héichstroumsignaler sinn komplett getrennt vun de schwaache Signaler vu klenge Stréim an Nidderspannungen. D'Héichspannungsdeeler sinn an alle Schichten ouni zousätzleche Koffer ausgehuewen. De Schleichdistanz tëscht den Héichspannungsdeeler gëtt no der Standardtabell iwwerpréift.

Den analoge Signal ass vum digitale Signal mat enger Divisiounsbreet vun op d'mannst 20mil getrennt, an den analoge Signal an den HF sinn an enger '-' Schrëft oder 'L' Form no den Ufuerderungen am modulare Design arrangéiert.

Den Héichfrequenzsignal ass vum Nidderfrequenzsignal getrennt, den Ofstand ass op d'mannst 3 mm, an de Kräizlayout kann net garantéiert ginn.

D'Layout vu Schlësselsignalgeräter wéi Kristalloszillator an Auertreiber soll wäit ewech vum Layout vum Interface-Schaltkrees sinn, net um Rand vun der Platin, an op d'mannst 10 mm vum Rand vun der Platin ewech. De Kristall an de Kristalloszillator solle beim Chip placéiert ginn, an der selwechter Schicht placéiert sinn, keng Lächer stéchen, a Plaz fir d'Äerd reservéieren.

Déi selwecht Strukturschaltung benotzt dat "symmetrescht" Standardlayout (direkt Wiederverwendung vum selwechte Modul) fir d'Konsistenz vum Signal z'erhalen.

Nom Design vun der PCB musse mir Analysen an Inspektioun maachen, fir d'Produktioun méi reibungslos ze gestalten.