層間静電容量が十分に大きくない場合、電界は基板の比較的広い領域に分散されるため、層間インピーダンスが低下し、リターン電流が最上層に逆流する可能性があります。この場合、この信号によって生成されたフィールドが、近くの変化する層信号のフィールドと干渉する可能性があります。これは私たちが望んでいたものではありません。残念ながら、0.062 インチの 4 層基板では、層間の距離が遠く、層間容量が小さくなります。

配線がレイヤー 1 からレイヤー 4、またはその逆に変更されると、図に示すような問題が発生します。

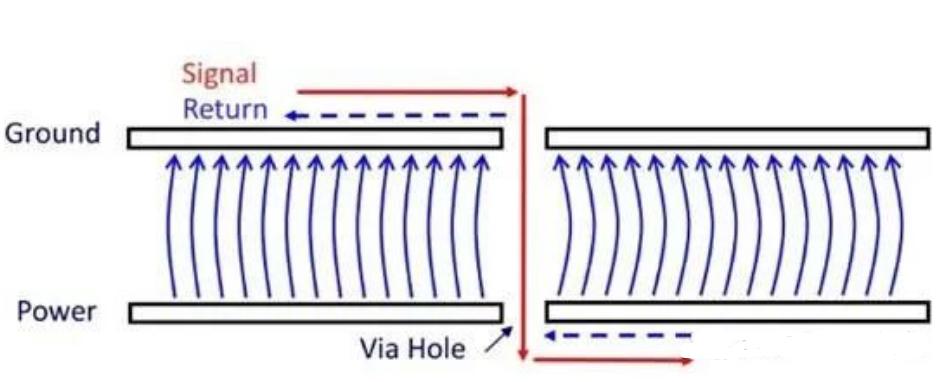

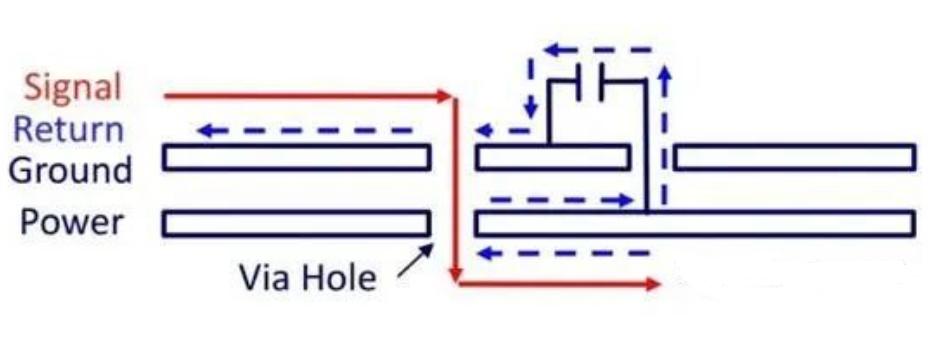

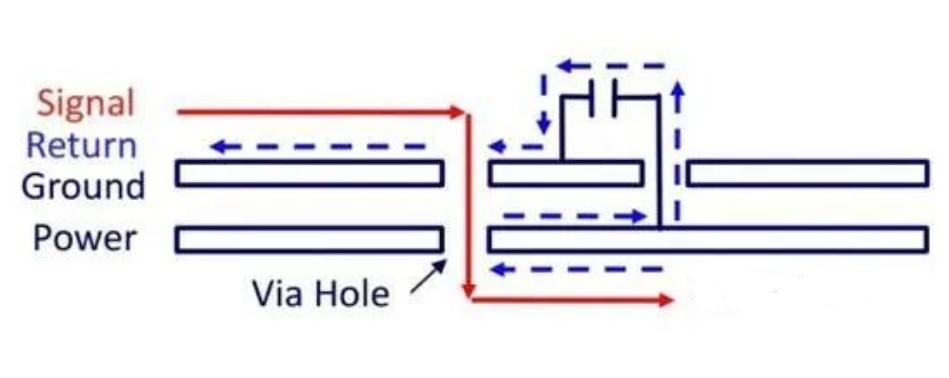

この図は、信号が層 1 から層 4 まで追跡するとき (赤い線)、リターン電流も平面を変更する必要がある (青い線) ことを示しています。信号の周波数が十分に高く、プレーンが互いに近接している場合、リターン電流はグランド層と電源層の間に存在する層間容量を通って流れる可能性があります。ただし、リターン電流のための直接の導電接続がないため、リターンパスは遮断されます。この遮断は、下の図に示すプレーン間のインピーダンスと考えることができます。

層間静電容量が十分に大きくない場合、電界は基板の比較的広い領域に分散されるため、層間インピーダンスが低下し、リターン電流が最上層に逆流する可能性があります。この場合、この信号によって生成されたフィールドが、近くの変化する層信号のフィールドと干渉する可能性があります。これは私たちが望んでいたものではありません。残念ながら、0.062 インチの 4 層基板では、層間の距離が遠く (少なくとも 0.020 インチ)、層間容量が小さくなります。その結果、上述した電界干渉が発生する。これによって信号の整合性の問題が発生することはありませんが、確実に EMI が増加します。このため、カスケードを使用するとき、特にクロックなどの高周波信号の場合、レイヤーの変更を避けます。

以下の図に示すように、戻り電流が受けるインピーダンスを低減するために、遷移パスホールの近くにデカップリング コンデンサを追加するのが一般的です。ただし、このデカップリング コンデンサは自己共振周波数が低いため、VHF 信号に対しては効果がありません。200 ~ 300 MHz を超える周波数の AC 信号の場合、低インピーダンスのリターン パスを作成するためにデカップリング コンデンサに依存することはできません。したがって、デカップリング コンデンサ (200 ~ 300 MHz 未満の場合) と、より高い周波数では比較的大きな基板間コンデンサが必要になります。

この問題は、キー信号のレイヤーを変更しないことで回避できます。しかし、4 層基板の基板間容量が小さいため、電力伝送という別の重大な問題が発生します。クロックデジタル IC は通常、大きな過渡電源電流を必要とします。IC 出力の立ち上がり/立ち下がり時間が短くなるにつれて、より高いレートでエネルギーを供給する必要があります。充電源を提供するために、通常、各ロジック IC のすぐ近くにデカップリング コンデンサを配置します。ただし、問題があります。自己共振周波数を超えると、これらの周波数ではコンデンサがインダクタのように動作するため、デカップリング コンデンサはエネルギーを効率的に保存したり転送したりできなくなります。

現在のほとんどの IC は立ち上がり/立ち下がり時間が速い (約 500 ps) ため、デカップリング コンデンサよりも高い自己共振周波数を持つ追加のデカップリング構造が必要です。回路基板の層間静電容量は、各層が互いに十分に近接して十分な静電容量を提供する場合、効果的なデカップリング構造となります。したがって、一般的に使用されるデカップリング コンデンサに加えて、デジタル IC に過渡電力を供給するために、密に配置された電源層とグランド層を使用することを好みます。

一般的な回路基板の製造プロセスにより、通常、4 層基板の 2 層目と 3 層目に薄い絶縁体が存在しないことに注意してください。2 層目と 3 層目の間に薄い絶縁体がある 4 層基板は、従来の 4 層基板よりもはるかに高価になる可能性があります。